AI晶片助陣 軟硬體整合 AIoT創新應用噴發

AI晶片助陣 創新應用噴發

導入邊緣運算裝置 可運用於零售流通、工業製造等各行各業 降低業者成本、提升服務品質

近兩年多來疫情改變眾多人生活模式,儘管各國目前已陸續走出疫情陰霾,但因疫情而衍生的各式便利遠距應用,仍將蓬勃發展。

其中在軟體面,為因應疫情而產生遠距居家上班的趨勢,促使如Hangouts Meet、Microsoft Teams、Zoom等視訊會議應用下載量大增,也讓社交視訊聊天程式如Houseparty的下載量呈現高度成長。因軟體面因素促使用者行為發生改變。

舉例來說,在工作、學習上相關應用方面如Spatial Systems這類的虛擬會議系統使用率增加。娛樂、社交相關應用方面,AR購物、VR線上遊戲、觀看賽事的使用比率也提升,也催生Amazon AR Shopping、NextVR的需求增加。

另外,為避免大多數人身體一有狀況即前往醫院檢測,造成醫療系統癱瘓,可居家偵測個人身體狀態的穿戴式裝置興起,如Kinsa IoT體溫計、可偵測人體血氧濃度的Fitbit Charge 4等產品也逐步擴大應用比例。又或是因為無法前往健身房,居家健身器材如使用Smart Mirror等裝置,導入連網機能的健身器材也大行其道。眾多創新的物聯網(IoT)產品,持續加速導入人們的日常當中。這是在疫情之下,終端市場出現的產品新契機。

其他如自動化無人運輸、智慧無人工廠等創新應用也如雨後春筍般紛紛出籠,各類型裝置使用先進半導體的機會將變得更為廣泛。且在5G與AI相結合下,不論是在雲端或是邊緣運算(Edge Computing)等領域,相比過往都需要更快的處理速度。

過往在雲端伺服器使用的AI晶片(AI on Chip)為講求運算功能,加上現今日益膨大的資訊處理量,致使晶片成本與耗電量水漲船高。而未來將會有愈來愈多的邊緣運算裝置布建在日常生活周遭,搭載AI on Chip機能的邊緣運算裝置,其應用場域將遍及零售流通業、醫療產業、工業製造、交通運輸、智慧城市與相關建設等。

可以預期的是,設置在工廠、零售服務業、汽車等場域等的感測器,未來將擷取大量感測資料並於邊緣運算(Edge Computing)裝置處理,透過交叉引用的方式可降低資料處理與應用成本,進而提升服務品質。

邊緣運算的需求正在迅速變化,晶片的研發課題在於如何持續提高晶片效能,降低功耗、並降低整體傳輸延遲以提高系統的可靠度。使用AI on Chip的邊緣運算晶片將與雲端主機機能整合,實現未來混合運算(hybrid computing)的基礎技術,也是台灣廠商著力的重點範疇。

5G、人工智慧驅動半導體產業快速成長,然複雜的運算亦帶來耗電的瓶頸。經濟部技術處帶領工研院提前布局,開發記憶體內運算與嵌入式記憶體技術,並與國內半導體大廠、美國加州大學洛杉磯分校合作,同時也獲得美國國防高等研究計畫署(DARPA)計畫支持,全力發展更快、更穩、更省電、關閉電源仍能保存數據的新世代記憶體。

而其效能媲美英特爾並領先三星,並解決記憶體陣列的干擾問題,為產業化邁進一大步,如應用在手機,手機使用人工智慧功能電量將從一天延長至逾三天,樹立新的新里程碑。未來透過異質封裝技術,可整合進先進製程處理器,在人工智慧、車用電子、高效能運算晶片等領域具有極佳的前景。

另外,技術處也結合國內半導體廠商成立「台灣人工智慧晶片聯盟」( AI-on-Chip Taiwan Alliance,AITA,簡稱愛台聯盟),並成立四大技術委員會(SIG),如今AITA國內外會員已達147家,聯盟會員在此溝通平台共議技術藍圖方向,國內半導體大廠也提供晶片研發,以及制訂技術共通介面,加速下世代半導體技術研發腳步,期透過產官學研通力合作,為台灣半導體產業再創下個經濟奇蹟。

(作者劉美君;經濟部技術處產業技術基磐研究與知識服務計畫成員)

軟體+硬體 穩固產業競爭力

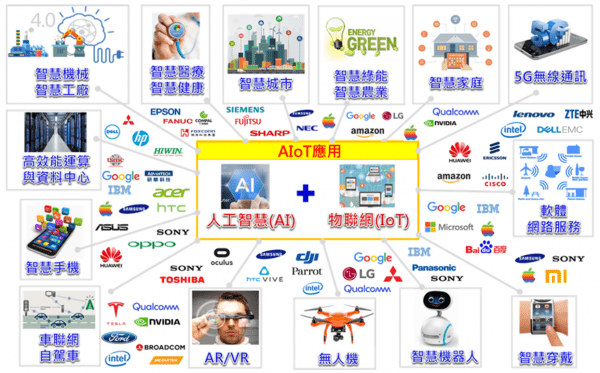

人工智慧無處不在,對各行各業的融入普及,將改變人們的生活方式。從產業發展的角度來看,AI已對現有的硬體、軟體、演算法、系統及商業模式帶來深刻的改變,影響廣泛,不僅是個人,也是社會、產業和政府,更成為國家競爭力的重要指標。

台灣半導體產業從萌芽之初即獲經濟部技術處扶植,培植出從半導體設計、製造到封測的護國神山群,成功打造出台灣在國際上不可取代的矽盾。如何將人工智慧與半導體晶片結合,創造更大優勢,則是產業面臨的挑戰。科技專案持續投入AI晶片軟硬體技術研發,未來將發揮軟硬整合的實力,讓台灣半導體產業繼續保持領先地位。

AI晶片的軟硬是不可分割,需要投入大量的軟體資源,而且缺乏標準規格和設計工具,這讓台灣過去以硬體為主、擅於按照標準快速開發晶片的企業感到頭痛,而設計門檻提高,也成為產業發展的挑戰。為解決此問題,工研院先行開發出AI晶片軟體設計平台,可協助業者迅速分析AI應用演算法以及最適合搭配的AI晶片硬體架構,以解決設計規格不確定的困境。

為讓AI演算法能在晶片硬體上更有效率的運行,工研院研發出國際一流的人工智慧晶片軟體編譯技術(AI Compiler),受到國際電子設計自動化龍頭大廠新思科技(Synopsys)肯定,在技術處支持下,工研院與新思科技共同成立人工智慧晶片設計實驗室,提供五大服務,包括晶片設計、軟體開發、系統驗證、教育訓練及產業諮詢等,此外,也透過公版設計平台(Reference Design)加速業者開發新AI晶片,縮短時程30%至50%,現在已服務多家廠商。

舉例來說,IC設計的新創公司創鑫智慧(Neuchips)在短短18個月成功開發的深度學習推薦模型(DLRM)加速晶片,是第一個以7奈米製程研發的國內雲端AI加速晶片。成功的背後,得益於人工智慧晶片設計實驗室的熱情協助,使原本計畫需由百人團隊耗時三至四年的時間,卻能以30人的團隊規模完成,把不可能變成可能。

隨著先進晶片製程逼近物理極限,晶片開發成本不斷攀升,產業進入後摩爾時代,小晶片(Chiplet)成為推動摩爾定律持續向前的解決方案之一,小晶片架構使晶片設計業者只需專注開發核心電路,再透過先進封裝技術,將其與外部不同製程IP整合在同一封裝內出售,可降低對於IC設計業者須採用先進製程下線(Tapeout)整個系統晶片(SoC)的負擔。

工研院與凌陽、鈺立微等IC設計廠商共同投入開發小晶片(Chiplet)共享智能運算架構,建立AI運算及感測周邊(C+P)晶片運算平台,形成AI小晶片系統設計環境,將有助於應用在AMR自主移動智慧機器人、智慧製造,智慧交通等領域。

另外,支援創新設計,全球首顆類比AI運算指紋辨識晶片,降低訊號轉換成數位資料儲存在記憶體中的步驟,可使類比AI以更低的能源將資料傳輸至中央處理器(CPU),並且由於低功耗運算與晶片成本的優勢,可為用戶帶來更好的使用體驗。技術處以科技專案協助IC設計大廠神盾及力旺,完成開發全球首顆可重組類比AI運算之屏下大面積光學指紋辨識晶片,該晶片能大幅提升指紋辨識率,並可導入手機、物聯網、汽車等終端應用。

近年政府持續為半導體產業擬定多元化發展策略,並與國內各大半導體廠相互合作,從產業技術研發到深入國際鏈結等方面展開,引導半導體持續創新,支持並投入半導體前瞻技術研發以滿足業界需求,推動AI晶片、下一代記憶體、小晶片系統、5G和6G高頻高功率電子、異質整合等半導體關鍵技術發展,期能為台灣再次建立更多的護國神山。

(作者張世杰;經濟部技術處AI on chip終端智慧發展計畫主持人)

異質整合 半導體業必修課

隨著人工智慧、人工智慧物聯網(AIoT)和5G科技的出現,台灣半導體晶圓代工模式也開始在全球聲名響亮,並站上國際供應鏈中的關鍵位置,且不斷推進半導體的先進製程。人工智慧和5G科技的不斷發展,使產業對於高階晶片的需求愈來愈急迫,因此具有高度晶片整合能力的異質整合封裝技術,被視為摩爾定律遭遇瓶頸後的動力,以持續推動半導體產業的發展。

人工智慧與5G科技產品對晶片封裝內不同電路訊號傳輸路徑更小、更大頻寬與更低耗電的需求日益增加,異質整合技術的發展將有助於晶片尺寸縮小、雜訊與散熱問題得以解決,也可以在高度整合下同步降低成本,因此,半導體業者已將加速推動高階晶片異質整合技術的發展作為當前的主要目標。

經濟部技術處長期支持與推動各項半導體關鍵技術的發展與交流,引導台灣半導體產業轉型升級,以應對異質整合帶來的產業升級進程中所面臨的壓力。考量台灣產業鏈分工的特色,以AI on Chip終端智慧發展計畫、可程式3D異質集成技術計畫以及AI晶片異質整合模組前瞻製造平台計畫等,藉多元的技術建構來協助升級台灣半導體產業。

為實現人工智慧的運算,必須要建立AI晶片與記憶體間的大量資料傳輸,科技專案支持工研院建立具有專利性的內嵌式高密度連線矽橋、與晶片金屬墊低溫直接接合等核心技術,以加強國內產業對人工智慧模組的資料傳輸連接線能力,這些技術與英特爾等國際公司相比,已具備領先或同步的地位,且已技轉給國內記憶體產業相關公司提升產品競爭力。

此外,由於裝置端人工智慧應用具有高彈性化與多樣化特性,創新系統要花費至少九個月時程進行客製化設計與製作驗證開發,因此常面臨無法掌握市場商機的困境。為此,工研院亦投入全球首見之內藏基板(EMAB)技術,並於2022年12月在日本半導體展首次發表,取得極高的肯定與回饋。

工研院的IC異質整合載板架構導入EMAB,具有多項優點:一、晶片可以使用可程式化的「矽橋(Silicon Bridge)」取代,可任意調整訊號方向與晶片組溝通。二、符合晶片整合多樣化的需求,並提供彈性與客製化的解決方案。三、以更有效的製程降低生產成本,開創全球半導體封裝領域的新手法,為國內系統公司提供創新開發的解決方案。

為滿足半導體製程不斷微縮、晶片面積增大的需求,在科技專案支持下,工研院投入相關製程技術研發與材料設備升級,強化異質整合技術開發,並與國內外半導體大廠攜手規劃成立「異質整合系統級封裝開發聯盟」,除可將大晶片切割成小晶片,以異質整合封裝技術將晶片相互整合,降低成本之外,更能解決散熱、訊號串接等挑戰。可以預見多維度的晶片設計與異質整合封裝架構,將是未來半導體關鍵利器。

此外,亦從封裝設計、測試驗證到小量產的技術服務等系統應用出發,提供AIoT系統應用平台與一站式服務,並隨著製程與檢測設備的到位,協助產業量產,達成供應鏈在地化的目標,與國際聯盟接軌,掌握半導體前進未來的動力。

(作者駱韋仲;經濟部技術處可程式3D異質集成技術計畫與AI晶片異質整合模組前瞻製造平台計畫成員)

本文同步刊登於2023/02/27經濟日報A10產業追蹤